Assignment

Lab Assignment 3 - Memories & Caches

Lab Assignment 3 - Memories & Caches

Completion requirements

In this assignment, we will revisit the concepts we learned during the memory hierarchy and memory management topics.

READ THE GUIDELINES BEFORE YOU START WITH YOUR ASSIGNMENT. READ EACH SECTION BEFORE YOU START WORKING ON IT.

The assignment is divided into 2 parts as follows:

Part 1 - Memory Hierarchy

We have a memory system where the register file contains 8 registers, each register can hold 16-bits. In the same system, a cache block is decided at 128 Bytes in size. The cache address contains 3 set bits. The cache, when half full, can hold a full page.

Answer the following questions then explain your answers:

Answers to this Part can be submitted using the online text box.

Part 2 - Memory Management and Data Propagation

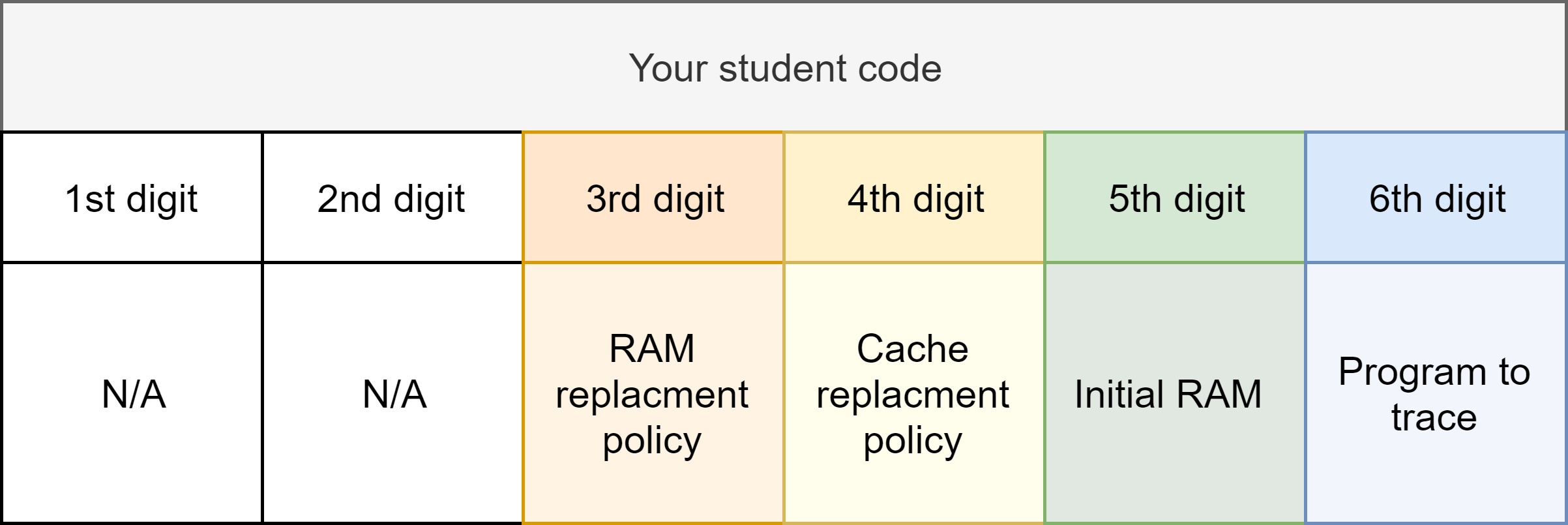

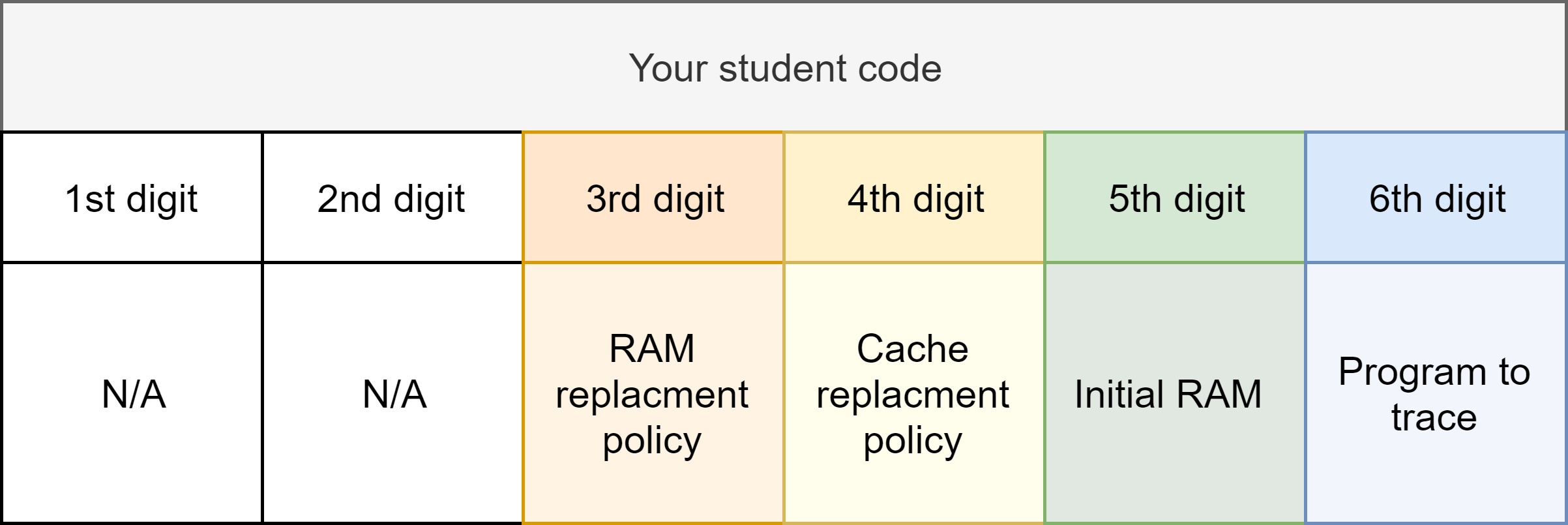

The following illustration shows how each digit will be used for this assignment:

The online assignment sheet will contain all the information you need to configure the assignment. From the assignment sheet, you can get which of the RAM and cache replacement policies to use, which initial RAM you have to start with, and what program to trace. The assignment sheet will be found here:

2- Failing to fill the Init tab in the Lab Assignment Trace Sheet.xlsx will cause point loss.

3- The tab assigned to you in the Init tab in the Lab Assignment Trace Sheet.xlsx must be completed before any other tabs can be accepted.

4- Your submission must be named FIRSTNAME_LASTNAME_STUDENTCODE.xlsx

Lab Assignment 3

In this assignment, we will revisit the concepts we learned during the memory hierarchy and memory management topics.

READ THE GUIDELINES BEFORE YOU START WITH YOUR ASSIGNMENT. READ EACH SECTION BEFORE YOU START WORKING ON IT.

The assignment is divided into 2 parts as follows:

Part 1 - Memory Hierarchy

We have a memory system where the register file contains 8 registers, each register can hold 16-bits. In the same system, a cache block is decided at 128 Bytes in size. The cache address contains 3 set bits. The cache, when half full, can hold a full page.

Answer the following questions then explain your answers:

1- What is the size of a page?

2- What is the size of the cache?

3- How many offset bits needed?

4- Which block, which set, and which word does this cache address refer to 0xfa2ed?

5- (This question is only for the IASM group) How many pages we can address using this memory system?

Answers to this Part can be submitted using the online text box.

Part 2 - Memory Management and Data Propagation

In this part, you will have to create RAM and cache traces. You will be using different replacement policies for RAM and for cache with different programs based on your student code.

SECTION 1: Initialization and Configuration set up

To ensure that students do not have the same lab assignment, you will use your student code to decide which RAM replacement policy, which cache replacement policy, which RAM to use, and which program to trace.

Your student code is made out of 10 characters. Four Letters that specifies your study program (MAHM, IASM). those four letters are irrelevant to this assignment. We will be using the six numbers that are in your student code. We will be using four of those digits to specify the configuration of your assignment. We will be using the last four digits of your student code as follows:

1- The first and second digits will not be used.

2- The third digit will specify which RAM replacement policy, FIFO or LRU, you will be using with your RAM.

3- The fourth digit will specify which Cache replacement policy, Direct Mapping or Fully associative or 2-way associative, you will be using with your cache.

4- The fifth digit will specify which RAM you will be using. Those initial RAMs will all be listed in the assignment sheet.

5- The sixth digit will specify which program you will be tracing, also specified in the assignment sheet.

https://docs.google.com/spreadsheets/d/1lu9VsK39w_ZEI6itRoQ-rL7UVjo95klLvqdmpaHbCT8/edit?usp=sharing

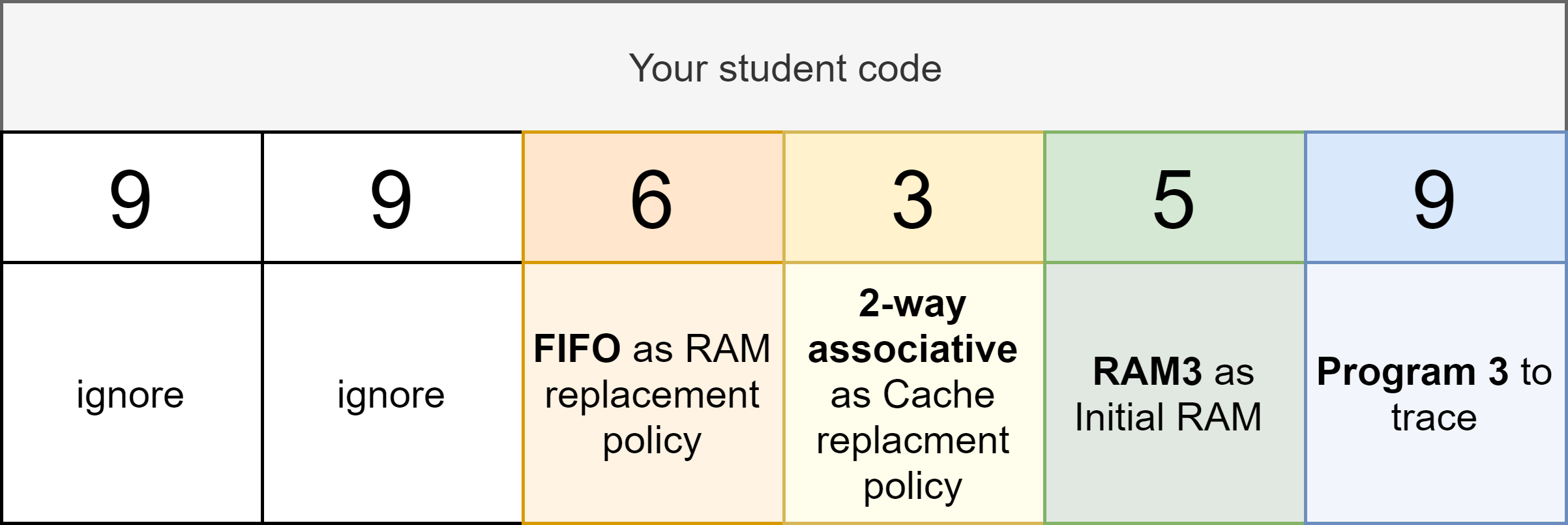

As an example of this, let us assume that a student had the following student code IASM 996359. This student will have the following configuration:

As for the cache, for all students, each cache is configured as follows:

1- The cache can fit 8 blocks.

2- The cache address has 4 offset bits.

3- The cache is initially empty. All the sets and ways are invalid.

SECTION 2: Tracing the RAM and Cache

In this section, the description of the assignment is provided.

What is required is the following:

1- Download the Lab Assignment Trace Sheet file attached to this assignment. The file has the tables you are required to fill. Those tables are similar to the tables you have filled during your Lab Activities in the past few weeks. The sheets are protected sheets, therefore many cells can not be edited or changed. You can only edit the cells that are relevant to you. In the Init tab, you must enter your name. If you enter the digits of your student code, the sheet will produce the configuration of your assignment for you. Note that in the Lab 3 Lab Assignment Trace sheet, there are four Tabs (Init, Direct Mapping, Fully associative, 2-way associative). You are only required to complete Init and the tab that is similar to your cache replacement policy. If you complete tabs that are different from the one assigned to you, you will only get extra points if the tab assigned to you is fully correct. If you do not complete the tab assigned to you, you will fail the assignment.

2- In the tab assigned to you, copy the complete program assigned to you from the online assignment sheet and paste it in the "addr" column in your Lab Assignment Trace Sheet.xlsx. Once you do that, the sheet will automatically divide all the addresses for you.3- In the execution column, you are required to indicate if the block (at addr) caused a miss or a hit when sent to the cache, similar to the lab activities. As shown in that column, you must perform two executions. Similar to the lab activities, complete the "Cache --- 1st execution" and "Cache --- 2nd execution" tables. Each row of those tables must fully reflect which block tags are in which set. Meaning that each row must be filled for each new block entering the cache. "Cache --- 2nd execution" is a continuation of the 1st execution. This means that the cache is not emptied when the 1st execution is over. Similarly, this is done for the RAM table.

4- The RAM table must be updated for each block. The online assignment sheet shows which page is each block is located in the RAM. If a block is being sent to the cache, the page that contains that block must be put in the RAM. If it is not, use the RAM replacement policy assigned to you to put that page in the RAM.

EXAMPLE: Say we want to put the block at address 0x4AE in the cache. From the online assignment sheet, we see that 0x4AE is located inside Page0000. This means that before we can put 0x4AE in the cache, we must check if Page0000 is in the RAM. If Page0000 is not in the RAM, we must move it there first. Once Page0000 is in the RAM, we then can move 0x4AE to the cache.

5- Once you copy your program to the sheet, it will be automatically decoded, use the decoded address to trace your cache. For the RAM trace, use the hexadecimal version of the address.

6- For the fully associative cache, use the Least Recently Used replacment policy.

7- Once done with both the executions. Save the sheet and attach it to your submission.

8- Once both executions, calculate the miss and hit rate of both of the executions in the online text.

Guidelines

1- The file must be submitted in the .xlsx format. Any other format will not be accepted.2- Failing to fill the Init tab in the Lab Assignment Trace Sheet.xlsx will cause point loss.

3- The tab assigned to you in the Init tab in the Lab Assignment Trace Sheet.xlsx must be completed before any other tabs can be accepted.

4- Your submission must be named FIRSTNAME_LASTNAME_STUDENTCODE.xlsx

If you have any questions, please post them on the Course participant's forum (ask questions from a teacher/other participants). Other students are encouraged to participate in asking and answering questions.

- 19 November 2020, 4:24 PM